**Research Article**

# Design and Implementation of Vedic Multipliers Using Reversible Logic Gates

### Ravi JN\*, Vijay Prakash AM and Madan S

Department of ECE, Bangalore Institute of Technology, Bangalore, India

## Abstract

Implementing the already existing circuits or new circuits using reversible logic has drawn a significant interest in recent years as a promising computing technique having application in low power CMOS, quantum computing, nanotechnology, optical computing ...etc. Reversible logic gates offer significant advantages such as high speed, low power, ease of fabrication ...etc. Also, circuits designed using these circuits would have better performance as compared to existing circuits. Main goals of reversible logic synthesis are to minimize the garbage, to minimize the delay, to minimize the total number of gates, to minimize the width of the circuit. In this paper, designer implemented 2 × 2 and 4 × 4 bit Vedic multipliers using reversible logic gate.

**Keywords:** Vedic multiplier; Reversible logic gates; Circuits; Power consumption

### Introduction

Basic concepts required to understand the reversible logic gates are described below:

### Why reversible logic gates?

When a computational system erases a bit of information, it must dissipate (kTln2) Joules of energy, where, 'k' is the Boltzmann's constant and 'T' is the temperature which has been proved experimentally. For T=300k (room temperature), this is about  $2.9 \times 10^{-21}$  Joules [1]. This is roughly the kinetic energy of a single air molecule at room temperature. Today's computers will erase a bit of information, every time they perform a logic operation. These logic operations are therefore called "Irreversible". This erasure is done very efficiently and much more than (kT) Joules of energy is dissipated for each bit erased. If we are to continue the revolution in computer hardware performance, we must continue to reduce energy dissipated by each logic operation. It can be reduced, by improving conventional methods, i.e., by improving the efficiency by reducing the power dissipated [2].

An alternative approach is to use logic operations that do not erase information. These are called "Reversible logic" operations and in practical applications they can dissipate arbitrarily less heat. As the energy dissipated per irreversible logic operation approaches the fundamental limit of (kTln2) Joules, the use of reversible operations is likely to become more attractive. Hence, if we wanted to reduce energy dissipation per logic operation, below (kTln2) Joules, we will be forced to use reversible logic [3].

### Basic reversible logic gates

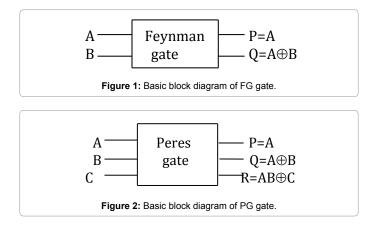

There are different types of reversible logic circuits are available. In this paper, author has used two of them, namely-Feynman gate (FG) and peres gate (PG) [4]. Boolean expressions for each of those two gates are shown in block diagrams below, at each output pins (Figures 1 and 2).

## Proposed Design Methodology

Different logic circuit can be realized by using reversible logic gates. This paper presents a better way to build a circuit which requires less power for its operation, lesser delay time...etc. Some of the design approaches for different logic circuits with reversible logic gates are below.

### Design and implementation of $2 \times 2$ and $4 \times 4$ bit vedic multiplier using irreversible logic gates

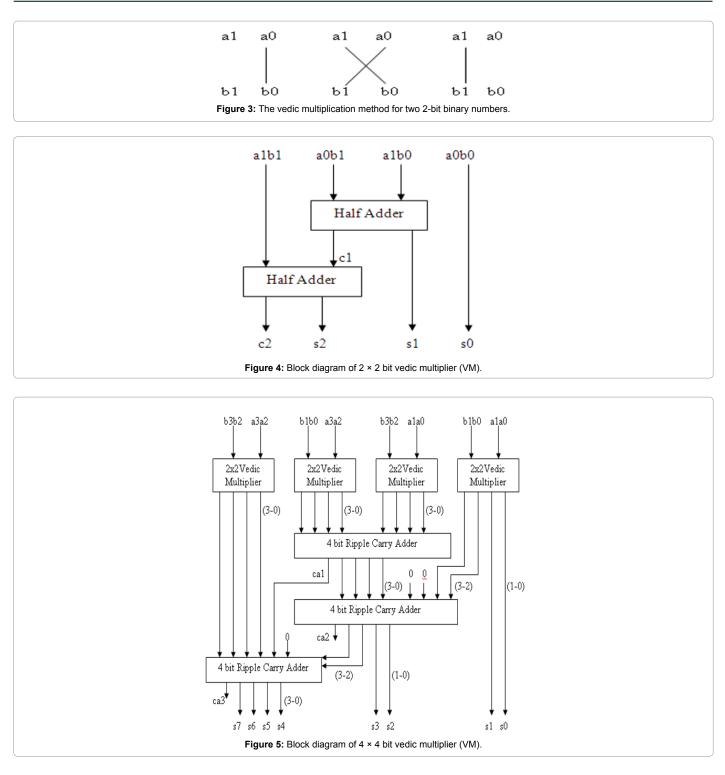

Vedic multiplier technique is used to perform multiplication operation in a faster way as compared to usual multiplication approach. In this paper we tried to implement the same not using irreversible gates but with reversible gates [5-7]. Basically,  $2 \times 2$  bit can be designed as shown in following figure, using irreversible logic gates. Then later peres gate is used as building block to gate to get Vedic multiplier (Figures 3 and 4).

Let A and B be 2 bit numbers which should be multiplied. Assuming each has bits as (a1a0) and (b1b0), we do following operation to get the product [8,9].

The final result will be c2s2s1s0. We can extend this procedure for higher bit multiplication using this  $2 \times 2$  bit VM as building block. Similarly block diagram for  $4 \times 4$  bit VM is shown below (Figure 5).

\*Corresponding author: Ravi JN, Department of ECE, Bangalore Institute of Technology, Bangalore, India, Tel: 08026615865; E-mail: ravijn095@gmail.com

Received March 02, 2017; Accepted April 02, 2018; Published April 09, 2018

**Citation:** Ravi JN, Vijay Prakash AM, Madan S (2018) Design and Implementation of Vedic Multipliers Using Reversible Logic Gates. J Electr Electron Syst 7: 255. doi: 10.4172/2332-0796.1000255

**Copyright:** © 2018 Ravi JN, et al. This is an open-access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited.

Page 2 of 5

# Design and implementation of $2 \times 2$ and $4 \times 4$ bit vedic multiplier using reversible logic gates

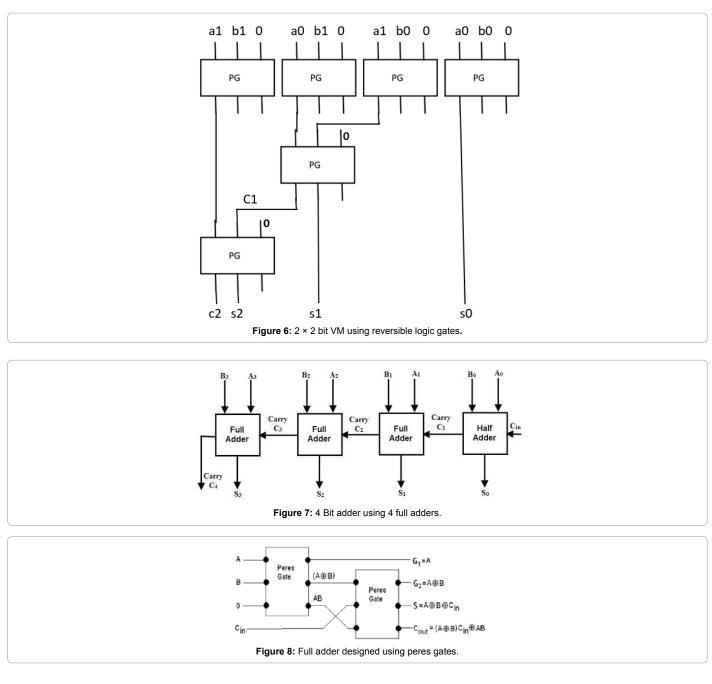

we will use  $2 \times 2$  bit VM. In general higher order bit VM can be implemented using  $2 \times 2$  bit VM as building block) (Figure 6).

Here we design VM using reversible logic gates, mainly we will use peres gate as building block to get VM.

As mentioned earlier circuits designed using reversible logic gates will consume less power [10]. Following figures shows the arrangement for  $2 \times 2$  and  $4 \times 4$  bit VM (in the case of  $4 \times 4$  bit multiplier design

In the case of  $4 \times 4$  bit VM we will use same block diagram as in Figure 2 with 4 bit ripple carry adder replaced with 4 bit adder using reversible gate (peres gate). Here 4 bit adder is implemented using peres gate which is used to realize full adder block as shown below (Figures 7 and 8).

Page 3 of 5

# **Results and Conclusion**

# Simulation results

| Reversible circuits | Delay (ns) | Power (mw) |

|---------------------|------------|------------|

| 2 × 2 VM            | 7.858      | 60         |

| 4 × 4 VM            | 13.839     | 60         |

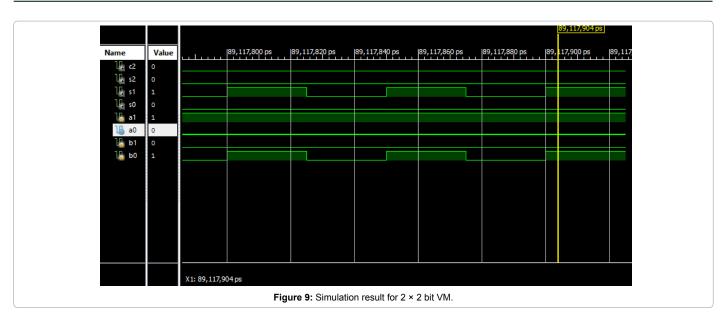

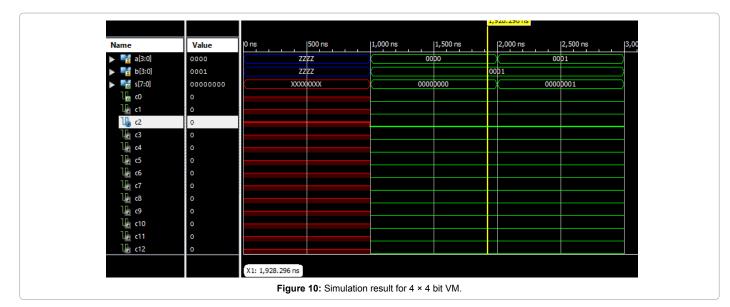

This section deals with the simulation results which are obtained for each circuit. The proposed circuits are simulated on Modalism tool and synthesized for Xilinx Spartan-3 with Device 3s4000fg208-5. For all the above mentioned circuits i.e.,  $2 \times 2$  and  $4 \times 4$  bit VM functionality is verified by using Xilinx ISE 13.1 software. Results can be easily verified with the help of waveforms for each case. Simulated snapshot input, output waveforms of the proposed circuits are shown from Figures 9 and 10.

# Synthesis results

Synthesis results for the above designed circuits are shown below in

Table 1: Delay and power consumption of designed circuits.

terms of delay generated out that circuit, power consumption. Results are simulated with the help of Xilinx software. Simulation results for 2 circuits discussed in this paper are shown below with the help of timing diagram using Xilinx software. Both circuits are tested for its functional correctness using Xilinx software. The simulation results are as shown in Tables 1-3.

### Conclusion

In this paper, author discussed about  $2 \times 2$  and  $4 \times 4$  bit VM

Page 4 of 5

| Selected Device        | 3s4000fg208-5(Spartan 3) |

|------------------------|--------------------------|

| Number of Slices       | 2 out of 2854 (0%)       |

| Number of 4 input LUTs | 4 out of 7168 (0%)       |

| Number of IOs          | 8                        |

| Number of bonded IOBs  | 8 out of 151 (5%)        |

| Selected Device        | 3s4000fg208-5(Spartan 3) |

|------------------------|--------------------------|

| Number of slices       | 23 out of 3584 (0%)      |

| Number of 4 input LUTs | 42 out of 7168 (0%)      |

| Number of IOs          | 17                       |

| Number of bonded IOBs  | 17 out of 141 (12%)      |

|                        |                          |

Table 2: Device utilization summary for 2 × 2 bit VM.

in terms of their respective power consumption and delay. Power consumption, delay generated, device utilization summaries for each of above mentioned is shown in Table 1. It can be observed that delay in our designed circuit is much lesser for 4 bit VM, compared to power delay analysis of CMOS multipliers using Vedic algorithm [8]. Similarly other parameters are obtained to be nearly equal to other design methodologies [7,8]. It has been seen that power consumption can reduced in the implementation of any logic circuit using reversible logic gate. Here, author simulated & synthesized the logic circuits using Xilinx software. Also, author implemented them by using peres gates, but other reversible gates can also be used for this purpose. Proposed

**Table 3:** Device utilization summary for  $4 \times 4$  bit VM.

circuits have applications in digital circuits like reversible processor, quantum computing, etc.

### References

- 1. Yelekar PR, Chiwande SS (2011) Introduction to Reversible Logic Gates and its Application. Int J Comput Appl, pp: 5-9.

- Nagarjun S, Nagendra R, Kiran KN (2014) Design and comparison of Reversible and irreversible sequential logic circuits. IJRAET 2: 13-19.

- Kanth BR, Krishna BM, Sirdhar M, Swaroop VGS (2012) A distinguish between reversible & conventional logic gates. IJERA 2: 148-151

- Ravi JN, Madan S (2017) Design & implementation of different digital components using reversible logic gates. IJTRS 2: 70-75.

### Page 5 of 5

- Thapliyal H, Ranganathan N (2010) Design of Reversible Sequential Circuits Optimizing Quantum Cost, Delay, and Garbage Outputs. ACM Journal on Emerging Technologies in Computer Systems.

- Verma P (2012) Design of 4 × 4 bit Vedic Multiplier using EDA Tool. Int J Computr Appl 48: 32-35.

- Jie LS, Ruslan SH (2016) A 2 × 2 bit VM with different adders in 90nm CMOS technology. AIP Conference Proceedings.

- 8. Kumari R, Mehra R (2016) Power delay analysis of CMOS multipliers using

vedic algorithm. IEEE International Conference on Power Electronics, Intelligent Control and Energy Systems.

- Premananda BS, Pai SS, Shashank B, Bhat SS (2013) Design and Implementation of 8-bit Vedic Multiplier. International Journal of Advanced Research in Electrical Electronics and Instrumentation Engineering 2: 5877-5882.

- Weste NHE, Harris DM (1998) CMOS VLSI Design: A Circuits and Systems Perspective, Pearson Publications, pp. 476-490.